Though this approach was not chosen due to complexity.įor a detailed explanation of this solution, check out Michael Park’s excellent blog post on constexpr function parameters”. To work around this limitation, a type template parameter can be used in conjunction with the newly introduced constexpr lambda (C++17). Perhaps ideally, we could have used something type-safe (perhaps std::optional) as our non-type template argument’s type, but this is not possible in C++17.

#IFORMAT EXAMPLE LW MIPS CODE#

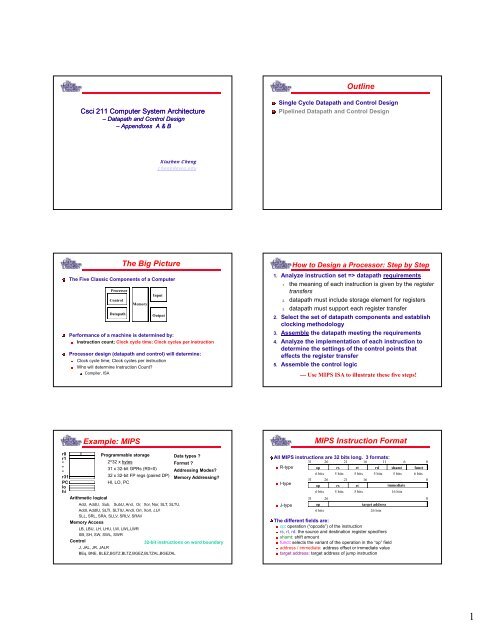

In this post, I mentioned the use of a sentinel value Arg used to special-case code generation for reading operands. Further Reading: constexpr Function Parameters The fixed 32-bit MIPS instruction may be encoded in one of three different formats depending on the number of operands, type of operands, and functionality of the instruction. It would have been possible to use variadic template arguments to handle both 2 and 3-tuples using a single function template, but this was decided against for simplicity. R & I-format Datapath The advanced datapath ADDI instruction LW.

The remaining field (not user-specifiable) will be std::nullopt ( RT in the case of bgez), though it will never be read as such, since no code will be generated to read it in the corresponding IType function template instantiation. I-Format Example (2/2) MIPS Instruction: addi 21,22,-50 82221 -50 001000 10110 10101. ITypeTuple implementation for 2-tuple operand strings. Typedef Instruction ( * EncodeFunc )( const Entry & ) std :: unordered_map inst_encoders = To keep all of the encoding rules in one place, the assembler supports the following declarative syntax: flags), used by the CPU to identify and configure itself for the instruction.ĭeclarative Instruction Encoding

#IFORMAT EXAMPLE LW MIPS MANUAL#

The figure (A.1) shows how the available 32 bits of an instruction are used by each of the three encoding formats.įrom IDT R30xx Family Software Reference Manual The three MIPS Instruction Encoding Formats the layout of its 32 bits) is dictated by the instruction’s format type, which is documented for all MIPS I instructions in the IDT R30xx Family Software Reference Manual. The proper machine encoding of the instruction (i.e. The assembler’s design supports multiple target architectures, but for now, I only need to support the MIPS I instruction set, which happens to be extremely convenient, in that it’s trivial to encode.Ī single MIPS assembler instruction is comprised of an operation mnemonic along with an optional operand list (e.g. It was my understanding that the reason you have to do the extra add instruction in the first solution, is actually because you cannot use a register as the offset.I recently started writing an assembler from scratch using C++17 for a somewhat obscure operating system. There are only three basic MIPS instruction formats: Register (as. What I'm confused about is my professor keeps saying that we can also do a lw instruction like this with 3 registers:Īre both of these solutions correct? Or is my instructor incorrect? You can't use a register for the offset can you? I thought the offset had to be an immediate number. space,36 (reserves and labels 36 bytes in memory and clears to 0). Assuming the base address of A is in register $s7 and the index (i) is in register $s1, I would have to do something along the lines of: Lw $rt, offset($rs) # where offset is an immediate value It is my understanding that the lw and sw operations are I-format instructions allowing 2 register operands, and one immediate operand: I am taking an architecture course currently and as part of that class I am learning MIPS assembly.

0 kommentar(er)

0 kommentar(er)